УДК 621.372.54

DOI: 10.25206/1813-8225-2023-188-152-161

**EDN: OJPIEK**

### В. В. ЕРОХИНС. А. ЗАВЬЯЛОВ

Омский государственный технический университет, г. Омск

# АВТОМАТИЗИРОВАННЫЙ СИНТЕЗ ТОПОЛОГИЙ ИНТЕГРАЛЬНЫХ СВЕРХВЫСОКОЧАСТОТНЫХ LC-ФИЛЬТРОВ С МИНИМИЗАЦИЕЙ ПОТЕРЬ В ПОЛОСЕ ПРОПУСКАНИЯ

В статье предложена разработанная методика автоматизированного синтеза топологий интегральных СВЧ LC-фильтров с минимизацией потерь в полосе пропускания путем минимизации длин межсоединений и поиска оптимальных топологий проводников, катушек индуктивности и конденсаторов. Предложены алгоритмы минимизации потерь и минимизации длины межсоединений LC-фильтров. Оптимизация топологий проводников, катушек индуктивности и конденсаторов происходит на основе верифицированных в кремнии моделей, учитывающих основные характеристики и ограничения технологического процесса, скин-эффект, краевые эффекты, влияния подложки и переходных отверстий. На основе методики разработана САПР в ПО MathCAD, применение которой позволило сократить время проектирования интегральных LC-фильтров до десятков минут, уменьшить потери в полосе пропускания фильтров на 1,1—2,7 дБ, увеличить крутизны фронтов и спадов АЧХ на 47—267 дБ/дек.

Ключевые слова: СВЧ, СнК, синтез фильтров, LC-фильтр, MathCAD, алгоритм оптимизации, методика.

1. Введение. LC-фильтры широко применяются в устройствах типа СнК (в технологических процессах Si, SiGe, GaAs), в частности в качестве входных фильтров сверхширокополосных СВЧ приемников. Потери во входном фильтре напрямую влияют на отношение сигнал/шум приемника, поэтому задача минимизации потерь в полосе пропускания (ПП) фильтра является важной и актуальной.

Одной из основных проблем при проектировании интегральных СВЧ LС-фильтров — это не достоверность моделей конденсаторов, катушек индуктивности и проводников, предоставляемых заводом-изготовителем. В моделях могут не учитываться скин-эффект, краевые эффекты, влияние подложки, вследствие чего модели не отражают реальных характеристик сосредоточенных элементов и проводников.

Минимизация потерь в полосе пропускания фильтров сводится к решению двух основных задач: максимизация добротностей катушек индуктивности и конденсаторов; минимизация потерь в проводниках межсоединений. В литературе представлены различные способы увеличения добротностей катушек индуктивности и уменьшения потерь в проводниках [1-11], в том числе использование нескольких параллельных слоев металлизаций, экранирование, травление подложки и др. Однако они имеют недостатки и ограниченную область эффективного применения, а также отсутствуют

методики, позволяющие оценить эффективность и найти оптимальную комбинацию этих способов для реализации топологии конкретного фильтра в конкретном технологическом процессе.

Целью данной работы является разработка методики автоматизированного синтеза топологий интегральных СВЧ LC-фильтров с минимизацией потерь в полосе пропускания.

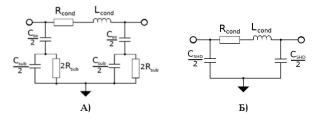

2. Минимизация потерь в проводниках. Для поиска оптимальной топологии проводника будет использована эквивалентная П-модель, представленная на рис. 1, которая верифицирована в технологическом процессе SiGe 130 нм [12, 13].  $L_{cond}$  — индуктивность проводника,  $R_{cond}$  — активное сопротивление с учетом скин-эффекта и сопротивлений переходных отверстий,  $C_{ox}$  — емкость между проводником и подложкой,  $C_{SHD}$  — емкость между проводником и заземленным экраном,  $C_{sub}$  и  $R_{sub}$  — емкость и сопротивление подложки.

Для расчета активного сопротивления на сверхвысоких частотах необходимо учитывать скинэффект, который заключается в том, что с ростом частоты плотность тока по проводнику распределяется неравномерно и ток протекает преимущественно в поверхностном слое материала проводника.

Для расчета сопротивления проводника с учетом скин-эффекта используются формулы (1-3) [14-15]:

$$R_{skin}(t, \rho, f) = \frac{\rho \cdot l_c}{W_c \cdot t_{eff}(t, \rho, f)}, \qquad (1)$$

где  $l_{_{c}}$  — длина проводника,  $w_{_{c}}$  — ширина проводника,  $\rho$  — удельное сопротивление проводника,  $t_{_{eff}}$  — эффективная толщина проводника:

$$t_{eff}(t, \rho, f) = \delta \cdot \left(1 - e^{-\frac{t}{\delta}}\right),$$

(2)

где t — физическая толщина проводника,  $\delta$  — толщина скин-слоя:

$$\delta(\rho, f) = \sqrt{\frac{\rho}{\pi \cdot \mu \cdot \mu_0 \cdot f}}, \qquad (3)$$

где  $\mu$ ,  $\mu_0$  — относительная магнитная проницаемость и магнитная проницаемость вакуума  $(4\pi\cdot 10^{-7})$ , f — частота.

Для нахождения минимально возможного сопротивления массива переходных отверстий между слоями металлизаций проводника была выведена формула (4) для нахождения максимально возможного количества переходных отверстий в проводнике шириной  $w_o$  и длиной  $l_o$ .

Сопротивление массива переходных отверстий рассчитывается по формуле (5).

$$N_{via} = \text{floor}\left[\left(\frac{w_c - 2c + b}{a + b}\right) \cdot \left(\frac{l_c - 2c + b}{a + b}\right)\right],\tag{4}$$

$$R_{via} = \frac{r_{via}}{N_{via}} \tag{5}$$

где  $N_{{\it via}}$  — количество переходных отверстий в массиве, функция floor(X) возвращает округленное значение X вниз до максимального целого,  $r_{{\it via}}$  — сопротивление одного переходного отверстия, a — ширина отверстия, b — минимальное расстояние между отверстиями, c — минимальное расстояние между отверстием и краем проводника.

Активное сопротивление проводника с учетом скин-эффекта и сопротивлений переходных отверстий рассчитывается по формуле:

$$R_{cond}(f) = \frac{1}{\frac{1}{R_{skin}(t_{n}, \rho_{n}, f)} + \sum_{i=1}^{m-1} \frac{1}{R_{skin}(t_{n-i}, \rho_{n-i}, f) + R_{vin}}},$$

(6)

где n — число слоев металлизации в технологическом процессе, m — число используемых слоев металлизаций.

Расчет индуктивности прямого проводника прямоугольного сечения осуществляется по формуле [16-19]:

$$L_{s}(w_{c}, I_{c}) = \frac{\mu_{0} \cdot I_{c}}{2\pi} \cdot \left[ \ln \left( \frac{2I_{c}}{w_{c} + t_{c}} \right) + 0,50049 + \frac{w_{c} + t_{c}}{3I_{c}} \right], \tag{7}$$

где  $t_{\scriptscriptstyle c}$  — толщина проводника. Так как силовые линии электромагнитного поля проводника, выполненного в нескольких слоях металлизации, не замыкаются вокруг каждого слоя, а замыкаются вокруг проводника, то толщину проводника для

Рис. 1. Модель интегрального проводника (А — без экрана, Б — с экраном)

расчета индуктивности необходимо рассчитывать по формуле:

$$t_c = \sum_{i=n-m+1}^{n} (t_i) + \sum_{i=n-m+2}^{n} (h_i - h_{i-1} - t_{i-1}), \tag{8}$$

где  $t_i$  и  $h_i$  — толщина и высота относительно подложки i-го слоя металлизации.

Для учета краевых эффектов конденсатора в данной работе будет использоваться формула Палмера [20], который аппроксимировал краевые эффекты плоского конденсатора методом Шварца—Кристоффеля для обкладок конечной длины и бесконечно малой толщины (9).

Формула Палмера имеет расхождение с моделированием методом конечных элементов не более 1,3 %, при этом технологический разброс диэлектрической проницаемости  ${

m SiO}_2$  может достигать более 5 %.

$$C_{edge}(h) = \frac{\varepsilon \cdot \varepsilon_0 \cdot w_c \cdot l_c}{h} \times \left(1 + \frac{h}{\pi \cdot l_c} + \frac{h}{\pi \cdot l_c} \cdot \ln\left(\frac{2\pi \cdot l_c}{h}\right)\right), \tag{9}$$

где  $\varepsilon_0=8.85\cdot 10^{-12}$  — электрическая постоянная,  $\varepsilon$  — диэлектрическая проницаемость диэлектрика между обкладками, h — толщина диэлектрика между обкладками. Паразитная емкость  $C_{ox}$  рассчитывается по формуле (9):

$$C_{ox} = C_{edge}(h_{ox})$$

,

где  $h_{ox}$  — толщина диэлектрика между проводником и подложкой, рассчитываемая по формуле (10). Для расчета  $C_{SHD}$  толщина диэлектрика между проводником и заземленным экраном в нижнем слое металлизации рассчитывается по формуле (11).

$$h_{ox} = h_{n-m+1}$$

(10)

$$h_{SHD} = h_{n-m+1} - t_1 - h_1$$

(11)

где  $h_{\it SHD}$  — толщина диэлектрика между проводником и экраном.

Для расчета паразитной емкости подложки используется формула (12), которая получена методом изображений и учитывает краевые эффекты [21-22].

$$C_{sub} = \frac{\varepsilon_{sub} \cdot \varepsilon_0 \cdot w_c \cdot l_c}{2t_{sub} + \sqrt{\frac{w_c \cdot l_c}{\pi}} - \sqrt{4t_{sub}^2 + \frac{w_c \cdot l_c}{\pi}}}$$

(12)

где  $\varepsilon_{sub}$  и  $t_{sub}$  — диэлектрическая проницаемость и толщина подложки.

Тестовые измерения емкостей и сопротивлений подложки показали, что формула (12) имеет большую погрешность только при площади проводника более 40000 мкм² [21].

При наличии металлизации с обратной стороны чипа паразитная емкость подложки рассчитывается по формуле (9), где за расстояние между обкладками нужно принять  $t_{sub'}$  а за диэлектрическую проницаемость —  $\varepsilon_{sub}$ .

Сопротивление подложки находится по формуле [22]:

$$R_{sub} = \frac{\rho_{sub} \cdot \varepsilon_{sub} \cdot \varepsilon_0}{C_{sub}}, \tag{13}$$

где  $\rho_{sub}$  — удельное сопротивление подложки.

Для оценки потерь проводника выведены формулы (14-18). Формулы (15-17) применимы для проводника без экрана, формула (18) — для проводника со сплошным заземленным экраном в нижнем слое металлизации под проводником.

$$Z2_{cond}(f) = R_{cond}(f) + i \cdot 2\pi \cdot f \cdot L_s(w_c, l_c), \tag{14}$$

$$Z_{ox}(f) = \frac{1}{i \cdot \pi \cdot f \cdot C_{odos}(h_{ox})},$$

(15)

$$Z_{sub}(f) = \frac{1}{i \cdot \pi \cdot f \cdot C_{sub}}.$$

(16)

$$Z1_{cond}(f) = Z_{ox}(f) + \frac{2Z_{sub}(f) \cdot R_{sub}}{2R_{sub} + Z_{sub}(f)}$$

, (17)

$$Z1_{cond}(f) = \frac{1}{i \cdot \pi \cdot f \cdot C_{odae}(h_{SHD})}$$

(18)

Матрица А-параметров проводника как четырехполюсника рассчитывается по формуле (19). Коэффициент передачи из матрицы А-параметров рассчитывается по известной формуле (20).

$$A = \begin{bmatrix} 1 + \frac{Z2_{cond}(f)}{Z1_{cond}(f)} & Z2_{cond}(f) \\ \\ \frac{2}{Z1_{cond}(f)} + \frac{Z2_{cond}(f)}{(Z1_{cond}(f))^2} & 1 + \frac{Z2_{cond}(f)}{Z1_{cond}(f)} \end{bmatrix}, (19)$$

$$K(f) = 20 \times \left( \frac{Z_{n2}}{A_{11} \cdot Z_{n2} + A_{12} + Z_{n1} \cdot (A_{21} \cdot Z_{n2} + A_{22})} \right), \quad (20)$$

где  $Z_{{}_{\!{\footnotesize H}}}$  и  $Z_{{}_{\!{\footnotesize H}^2}}$  — сопротивления источника сигнала и нагрузки соответственно.

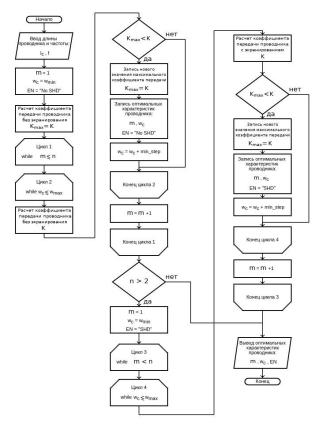

На рис. 2 представлен разработанный алгоритм расчета оптимальной топологии проводников межсоединений (на основе верифицированной модели проводника) при заданной длине проводника и частоте, на которой требуется оптимизация. Топология проводника оптимизируется по критерию получения максимального коэффициента передачи на заданной частоте.

$w_{\min}$ ,  $w_{\max}$ ,  $min\_step$  — ограничения технологического процесса: минимальная ширина, максимальная ширина, минимальный шаг изменения длины и ширины проводника соответственно. Перемен-

Рис. 2. Алгоритм расчета оптимальной топологии проводника

ная *EN* характеризует наличие ("SHD") или отсутствие ("NoSHD") заземленного экрана под проводником.

В циклах 1 и 3 рассчитывается оптимальное количество используемых слоев металлизаций при заданной ширине проводника без использования экрана и с экраном соответственно. В циклах 2 и 4 рассчитываются оптимальные ширины проводника при заданном количестве используемых слоев металлизаций без использования экрана и с экраном соответственно. Таким образом, находится топология проводника с минимальными потерями на заданной частоте (наивысшей частоте полосы пропускания), а также решается задача целесообразности использования экранирования под проводником.

Разработанный алгоритм реализован в качестве программы в ПО MathCad. Расчет оптимальной топологии занимает доли единицы секунд.

3. Минимизация длины проводников межсоединений. Длина межсоединений в LC-фильтре зависит от конфигурации фильтра, габаритов сосредоточенных элементов и минимального расстояния между сосредоточенными элементами.

Минимальное расстояние между катушками индуктивности предлагается принять расстоянию, на котором их взаимная индуктивность будет менее 1 % от полных индуктивностей катушек. Анализ экспериментальных образцов фильтров показал, что при таких расстояниях можно пренебречь их взаимной индуктивностью, и это не оказывает влияния на АЧХ фильтра.

Для двух восьмиугольных или круглых катушек индуктивности взаимная индуктивность между катушками будет меньше, чем у квадратных, поэтому для упрощения расчетов минимальное расстояние между ними будет рассчитываться как для квадратных катушек.

Для упрощенного расчета взаимной индуктивности двух одинаковых катушек ограничим топологию катушек только полными витками. Наиболее точным методом расчета индуктивности является метод, заключающийся в разбиении катушки на прямоугольные сегменты и расчете всех собственных и взаимных индуктивностей всех сегментов [16—19].

Собственные индуктивности сегментов катушки рассчитываются по формуле (7), где длина сегментов i-го витка рассчитывается по формуле:

$$I_{sea}(i) = d_{in} + w + 2i(w + s), \tag{21}$$

где  $d_{\it in}$  — внутренний диаметр катушки, w — ширина витка, s — зазор между витками.

Взаимная индуктивность параллельных сегментов одинаковой длины рассчитывается по формуле [9-12]:

$$M(w, l, d) = \frac{\mu_0}{2\pi} \cdot l \cdot Q(w, l, d)$$

(22)

где d — расстояние между сегментами, l — длина сегментов, Q(w, l, d) — параметр взаимной индуктивности, характеризующий удельную взаимную индуктивность на единицу длины проводника:

$$Q(w, l, d) = \ln \left[ \frac{l}{GMD(w, d)} + \sqrt{1 + \left(\frac{l}{GMD(w, d)}\right)^2} \right] - \sqrt{1 + \left(\frac{GMD(w, d)}{l}\right)^2} + \frac{GMD(w, d)}{l},$$

(23)

где GMD(w, d) — среднегеометрическое расстояние между сегментами:

$$GMD(w,d) = \exp \begin{bmatrix} \ln(d) - \frac{w^2}{12d^2} - \frac{w^4}{60d^4} - \\ -\frac{w^6}{168d^6} - \frac{w^8}{360d^8} - \frac{w^{10}}{660d^{10}} \end{bmatrix}. (24)$$

При сонаправленности векторов протекания тока в сегментах взаимная индуктивность будет иметь положительный знак, при разнонаправленности — отрицательный.

Взаимная индуктивность параллельных сегментов разной длины (l и m) и одинаковой ширины (w) рассчитывается по формуле [9-12]:

$$M_{dls}(w, l, m, d) = M\left(w, \frac{l+m}{2}, d\right) - M\left(w, \frac{|l-m|}{2}, d\right).$$

(25)

Тогда взаимная индуктивность i-го и p-го полных витков одной катушки будет находиться по формулам:

$$M_{coils}(i, p) = 8 \cdot M_{dts}(w, l_{seg}(i), l_{seg}(p), d_{pos}(i, p)) - 8 \cdot M_{dts}(w, l_{seg}(i), l_{seg}(p), d_{neg}(i, p)),$$

(26)

$$d_{pos}(i,p) = (|i-p|) \cdot (w+s), \qquad (27)$$

$$d_{neg}(i, p) = d_{in} + 2\min(i, p) \cdot (w + s) + w + d_{neg}$$

(28)

где  $d_{{\it pos}}$  — расстояния между сегментами разных витков с положительной взаимной индуктивностью,  $d_{{\it neg}}$  — с отрицательной.

Полная индуктивность каждой из катушек рассчитывается по выведенной формуле:

$$L_{full} = \sum_{i=1}^{N} \left[ 4 \cdot L_{s}(w, I_{seg}(i)) + \sum_{n=1}^{N} \left( \frac{M_{coils}(i, n)}{2} \right) \right], (29)$$

где N — количество витков катушки.

Для расчета взаимной индуктивности двух одинаковых квадратных катушек индуктивности, находящихся на расстоянии X, были выведены формулы (30-33).

$$\begin{split} M_{ind} &= \\ &= 2 \cdot \sum_{i=1}^{N} \sum_{p=1}^{N} \left[ 2M_{dls} \left( w, l_{seg}(i), l_{seg}(p), d_{pos1}(i, p) \right) + \\ &+ 2M_{dls} \left( w, l_{seg}(i), l_{seg}(p), d_{pos2}(i, p) \right) - \\ &- 4M_{dls} \left( w, l_{seg}(i), l_{seg}(p), d_{neg}(i, p) \right) \right], \end{split} \tag{30}$$

$$d_{post}(i, p) = X + w + (w + s) \cdot (2N - i - p), \tag{31}$$

$$d_{pos2}(i,p) = X + 2d_{in} + 3w + (w+s) \cdot (2N+i+p), (32)$$

$$d_{neg}(i, p) = X + 2w + (w + s) \times \times (2N - i - p) + d_{in} + 2\max(i, p) \cdot (w + s),$$

(33)

где  $d_{pos}(i,p)$  — расстояния между сегментами i-го витка одной катушки и p-го витка второй катушки с положительной взаимной индуктивностью,  $d_{neg}(i,p)$  — с отрицательной.

Коэффициент, отражающий отношение взаимной индуктивности двух катушек индуктивности и их полных индуктивностей рассчитывается по формуле:

$$k_{ind} = \frac{M_{ind}}{2 \cdot L_{total}} \cdot 100 \%. \tag{34}$$

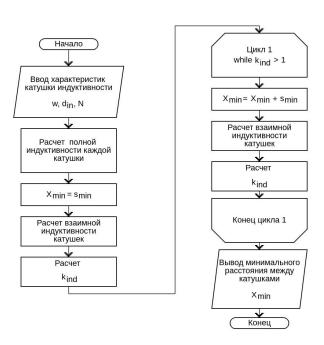

Рис. 3. Алгоритм поиска минимального расстояния между катушками индуктивности

Рис. 4. Алгоритм автоматизированного расчета оптимизированных интегральных LC-фильтров

Разработанный алгоритм поиска минимального расстояния между катушками индуктивности представлен на рис. 3. Минимальное расстояние между двумя катушками с разной топологией выбирается большее из двух, рассчитанных по предложенному алгоритму  $s_{\min}$  — минимальное расстояние между проводниками (ограничение технологического процесса),  $X_{\min}$  — рассчитанное минимальное расстояние между катушками.

Предложенная методика поиска минимального расстояния между катушками позволяет определить минимальные длины проводников межсоединений при исключении влияния паразитных взаимных индуктивностей между катушками индуктивности.

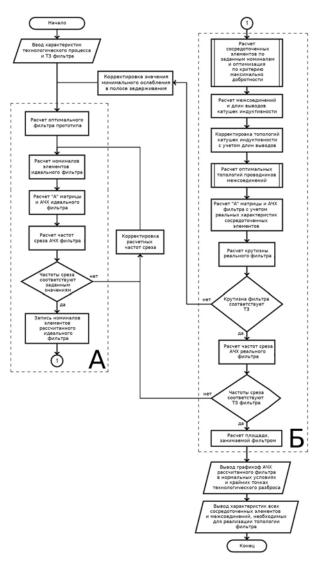

4. Автоматизированный синтез топологий интегральных LC-фильтров. Разработанный алгоритм автоматизированного синтеза интегральных LC-фильтров с минимизацией потерь в полосе пропускания представлен на рис. 4.

В блоке "А" рассчитываются номиналы элементов идеального фильтра (фильтра с идеальными конденсаторами, катушками индуктивности без учета проводников межсоединений). Принципиальная схема фильтра и номиналы элементов рассчитываются по фильтрам-прототипам эллиптических ФНЧ, представленным во множестве источников, в том числе в справочниках по расчету фильтров

авторов Зааль Р. и Ханзел Г. [23—24]. Выбирается фильтр-прототип, соответствующий техническому заданию и имеющий минимальный порядок и минимальную неравномерность в полосе пропускания.

Для построения АЧХ необходимо найти матрицу А-параметров (АВСD-матрицу) фильтра, которая рассчитывается согласно теории простых и сложных четырехполюсников [25]. Коэффициент передачи фильтра рассчитывается по формуле (20).

В блоке "Б" рассчитывается топология реального фильтра с оптимизированными топологиями катушек индуктивности, конденсаторов, проводников межсоединений. Оптимизация топологий катушек индуктивности, конденсаторов не рассматривается в данной работе. Проводники межсоединений оптимизируются по критерию наибольшего коэффициента передачи на наивысшей частоте полосы пропускания.

Ввиду ограниченных добротностей реальных интегральных катушек индуктивности, конденсаторов и потерь в проводниках межсоединений, АЧХ реального фильтра может отличаться от АЧХ идеального фильтра. Для получения характеристик реального фильтра в рамках требований технического задания в алгоритме предусмотрены корректировки частот среза и крутизны фильтра.

Поиск минимального ослабления в полосе пропускания и частоты, при которой достигается минимальное ослабление, осуществляется методом равномерного поиска в диапазоне заданных техническими требованиями частот среза фильтра с заданным шагом k/2. Частоты среза определяются методом равномерного поиска от частоты, при которой достигается минимальное ослабление, до частоты, при которой ослабление увеличивается на 3 дБ относительно минимального.

Корректировка расчетных частот среза происходит по формуле (35) до момента, пока частоты среза АЧХ не будут находиться в диапазоне заданного значения с заданной точностью ( $f_0 \pm k/2$ ).

$$f_{new} = \frac{f_0 \cdot f_{old}}{f_{sr}},\tag{35}$$

где  $f_0$  — частота среза, заданная техническим заданием;  $f_{old}$  — расчетное значение частоты среза до корректировки,  $f_{sr}$  — частота среза, найденная по АЧХ фильтра до корректировки,  $f_{new}$  — расчетное значение частоты среза после корректировки.

После корректировки частот среза происходит перерасчет номиналов элементов идеального фильтра и оптимизация топологии фильтра для новых номиналов элементов.

Ослабление в полосе задерживания относительно полосы пропускания синтезированного фильтра рассчитывается по формуле (36) для ФНЧ и по формуле (37) для ФВЧ.

$$As_{LPF} = \left| K \left( \frac{f_{sr\_LPF}}{\Omega s_{LPF}} \right) - K_{\text{max}} \right|, \tag{36}$$

$$As_{HPF} = \left| K \left( \Omega s_{HPF} \cdot f_{sr\_HPF} \right) - K_{\text{max}} \right|, \tag{37}$$

где  $K_{\max}$  — максимальный коэффициент передачи в полосе пропускания;  $f_{\rm sr}$  — найденная по АЧХ частота среза реального фильтра;  $\Omega s$  — нормированные границы полос задерживания.

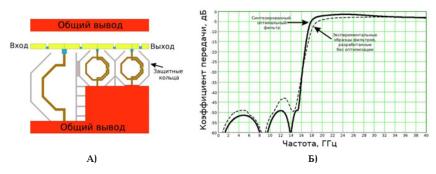

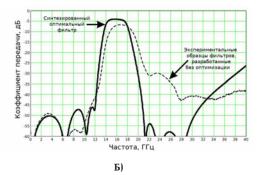

Рис. 5. Топология (А) и АЧХ (Б) синтезированного ФВЧ 18 ГГц

Таблица 1

#### Сравнение характеристик ФВЧ 18 ГГц

| Характеристика                                      | Синтезированный<br>оптимальный фильтр | Экспериментальные образцы неоптимизированного фильтра | ТЗ           |

|-----------------------------------------------------|---------------------------------------|-------------------------------------------------------|--------------|

| Частота среза, ГГц                                  | 18,04 - 18,05                         | 18,8 – 18,9                                           | $18 \pm 0.1$ |

| Минимальное ослабление в ПП, дБ                     | 1,4-1,5                               | 2,6-2,8                                               | _            |

| Ослабление на частоте 15 ГГц относительно<br>ПП, дБ | 47,5 – 47,9                           | 43,8 – 44,0                                           | ≥ 40         |

| Крутизна фронта АЧХ, дБ/дек.                        | 371 – 374                             | 324 – 325                                             | ≥ 333        |

| Ослабление на частоте 40 ГГц, дБ                    | 2,9-3,1                               | 3,4                                                   | _            |

| Занимаемая площадь, мм²                             | 0,31                                  | 0,29                                                  | _            |

Крутизна АЧХ фильтра определяется по формулам (38—39) между двумя точками АЧХ: на частоте среза и на границе полосы задерживания.

$$g_{LPF} = \frac{10}{\Omega s_{LPF}} \cdot \left| K \left( f_{sr\_LPF} \right) - K \left( f_{sr\_LPF} \cdot \Omega s_{LPF} \right) \right|, \quad (38)$$

$$g_{HPF} = 10 \cdot \Omega s_{HPF} \cdot \left| K \left( f_{sr\_HPF} \right) - K \left( \frac{f_{sr\_HPF}}{\Omega s_{HPF}} \right) \right|, \quad (39)$$

где  $g_{{\scriptscriptstyle HPF}}$  и  $g_{{\scriptscriptstyle LPF}}$  — крутизны фронта и спада АЧХ соответственно [дБ/дек].

Если рассчитанное ослабление в полосе задерживания меньше значения, заданного техническим заданием, то необходимое значение ослабления увеличивается на разницу между ослаблением в реальном фильтре и ослаблением, заданным в ТЗ. Так осуществляется поправка крутизны фильтра для технологического процесса, в котором синтезируется фильтр, с учетом потерь в полосе пропускания.

Корректировка крутизны происходит один раз при первом расчете реального фильтра. После корректировки необходимого ослабления в полосе задерживания находится новый оптимальный фильтр-прототип, удовлетворяющий требованиям ТЗ, с учетом поправок на технологический процесс, перерасчет номиналов элементов идеального фильтра и оптимизация топологии фильтра для новых номиналов элементов.

Выходными данными разработанного алгоритма являются: площадь, занимаемая ядром синтезированного фильтра без учета площади проводников общего вывода; все характеристики топологий катушек индуктивности, конденсаторов и проводников межсоединений, необходимые для реализации этой топологии.

Разработанный алгоритм реализован в качестве САПР автоматизированного синтеза оптимальной топологии СВЧ фильтра в среде MathCAD [26]. В программе для наглядности рассчитываются графики АЧХ синтезированного реального фильтра в нормальных условиях и крайних точках разброса технологического процесса. Автоматизированный синтез оптимальной топологии фильтра занимает единицы минут.

5. Синтезированные оптимальные СВЧ LС-фильтры. Для оценки эффективности автоматизированного синтеза с минимизацией потерь в полосе пропускания сравним АЧХ синтезированного оптимального фильтра с АЧХ экспериментальных образцов фильтров, выполненных в технологическом процессе SiGe 130 нм. Процесс имеет 6 медных слоев металлизации, из которых четыре нижних имеют толщину 0,4 мкм, а два верхних — 3,2 мкм, толщина диэлектрика между слоями металлизаций и подложки составляет от 1 до 8 мкм, удельное сопротивление подложки не более 0,5 Ом·м.

Разработанная топология и АЧХ синтезированного ФВЧ 18 ГГц (эллиптический фильтр 7-го порядка) представлена на рис. 5. Для сравнения характеристик синтезированного фильтра с техническим заданием и характеристиками экспериментальных образцов не оптимального фильтра данные сведены в табл. 1. Характеристики синтезированного фильтра приведены в крайних точках технологического разброса.

В фильтрах, реализованных в технологических процессах Si, SiGe и других технологических процессах, с удельным сопротивлением подложки менее 10 [Ом·м], паразитные каналы связи через подложку между сосредоточенными элементами и проводниками межсоединений оказывают значительное влияние на добротность элементов и АЧХ фильтров [27—28]. Для исключения влияния

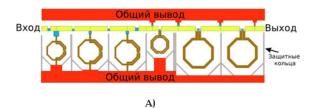

Рис. 6. Топология (А) и АЧХ (Б) синтезированного ПФ 14-18 ГГц

Таблица 2

#### Сравнение характеристик ПФ 14-18 ГГц

| Характеристика                                      | Синтезированный<br>оптимальный фильтр | Экспериментальные образцы неоптимизированного фильтра | ТЗ     |

|-----------------------------------------------------|---------------------------------------|-------------------------------------------------------|--------|

| Нижняя частота среза, ГГц                           | 13,96 – 13,98                         | 14,5 – 14,8                                           | 14±0,1 |

| Частота среза, ГГц                                  | 17,96 – 18,02                         | 18,9 – 19,1                                           | 18±0,1 |

| Минимальное ослабление в ПП, дБ                     | 4,0-4,4                               | 6,7-6,9                                               | -      |

| Ослабление на частоте 11 ГГц<br>относительно ПП, дБ | 44,4-44,9                             | 39,2-39,4                                             | ≥ 40   |

| Крутизна фронта АЧХ, дБ/дек.                        | 325 – 329                             | 271 – 273                                             | ≥ 314  |

| Ослабление на частоте 21 ГГц, дБ                    | 49,3-51,0                             | 19,4 – 20,1                                           | ≥ 40   |

| Крутизна спада АЧХ, дБ/дек.                         | 397 – 411                             | 149-154                                               | ≥ 343  |

| Занимаемая площадь, мм <sup>2</sup>                 | 0,44                                  | 0,29                                                  | -      |

паразитных каналов связи через подложку для интегральных катушек индуктивности и конденсаторов, используемых в СВЧ устройствах, применяют защитные кольца, выполненные в нижнем слое металлизации с переходными отверстиями к подложке, подключенные к общему выводу [27-28]. Использование короткозамкнутых защитных колец уменьшает индуктивность и добротность катушек, но результаты исследований, опубликованные в [29-30], показывают, что использование не замкнутых заземленных защитных колец позволяет значительно уменьшить влияние паразитных каналов связи через подложку, сохранив при этом индуктивность и добротность катушек индуктивности. Влияние паразитных каналов связи через подложку на АЧХ фильтра при отсутствии заземленных защитных колец описано в статье [13].

По данным табл. 1 видно, что синтезированный оптимальный фильтр по сравнению с характеристиками не оптимального фильтра соответствует техническому заданию, имеет минимальное ослабление в полосе пропускания на 1,1 дБ меньше, имеет крутизну на 47 дБ/дек больше, площадь фильтра при этом увеличилась незначительно.

Синтезированная топология  $\Pi\Phi$  14—18  $\Gamma\Gamma\Pi$  с минимизацией потерь в полосе пропускания представлена на рис. 6. Фильтр является каскадным соединением эллиптических ФВЧ и ФНЧ 7-х порядков. Сравнительные характеристики сведены в табл. 2.

Видно, что синтезированный оптимальный фильтр имеет потери в полосе пропускания на 2,5—2,7 дБ меньше, крутизну фронта АЧХ на 54—56 дБ/дек больше, крутизну среза АЧХ на 248—267 дБ/дек больше, чем фильтр, разработанный без

оптимизации топологий катушек индуктивности, конденсаторов, проводников.

6. Заключение. Предложен алгоритм поиска оптимальной топологии проводника по критерию максимального коэффициента передачи на требуемой частоте. В процессе оптимизации проверяется целесообразность использования заземленного экрана под проводником, применение которого уменьшает потери интегральных проводников путем исключения влияния подложки с относительно низким удельным сопротивлением.

Предложена методика поиска минимального расстояния между катушками, которая позволяет минимизировать длину проводников межсоединений, следовательно, уменьшить потери в полосе пропускания фильтров, при этом исключая влияние паразитных взаимных индуктивностей между катушками фильтра.

Предложена методика синтеза топологий интегральных СВЧ LC-фильтров с минимизацией потерь в полосе пропускания. На основе предложенной методики разработано САПР синтеза оптимальных топологий интегральных СВЧ LC-фильтров в ПО MathCad.

Выявлено, что синтезированные оптимальные фильтры по предложенной методике имеют потери в полосе пропускания на 1,1-2,7 дБ меньше, крутизны фронтов и спадов АЧХ на 47-267 дБ/дек больше, чем экспериментальные образцы ранее разработанных фильтров без оптимизации. Также выявлено, что синтезированные оптимальные фильтры имеют на порядок меньший разброс частот среза в крайних точках технологического разброса, что значительно повышает повторяемость характеристик производимых фильтров.

Синтезированные ПФ 14-18 ГГц и ФВЧ 18 ГГц с минимизацией потерь в полосе пропускания были использованы в качестве сложнофункциональных блоков в сверхширокополосных СВЧ приемниках типа СнК, разработанных в рамках НИОКР  $\mathbb{N}$  AAAA-A20-120073190008-5 от 31.07.2020.

С использованием предложенной методики в рамках НИР № 122091300037-0 от 13.09.2022 разработаны LC-фильтры, применяемые в качестве СФ-блоков модулятора телевизионных сигналов с выходным частотным диапазоном 1—1,4 ГГц. Производство интегральной микросхемы было выполнено за счет средств Минобрнауки России в рамках федерального проекта «Подготовка кадров и научного фундамента для электронной промышленности» по государственному заданию на выполнение научно-исследовательской работы «Разработка методики прототипирования электронной компонентной базы на отечественных микроэлектронных производствах на основе сервиса МРW (FSMR-2023-0008)».

#### Библиографический список

- 1. Kim J., Plouchart J. K., Zamdmer N. [et al.]. High-Performance Three-Dimensional On-chip Inductors in SOI CMOS Technology for Monolithic RF Circuit Applications // Radio Frequency Integrated Circuits (RFIC) Symposium, 2003 IEEE. 2003. P. 591-594. DOI: 10.1109/RFIC.2003.1214016.

- 2. Danesh M., Long J. R. Differentially Driven Symmetric Microstrip Inductors // IEEE Transactions on Microwave Theory and Techniques. 2002. Vol. 50, Issue 1. P. 332-341. DOI: 10.1109/22.981285.

- 3. Chen J., Liou J. J. Improved and Physics-Based Model for Symmetrical Spiral Inductors // IEEE Transactions on Electron Devices. 2006. Vol. 53, Issue 6. P. 1300 1309. DOI: 10.1109/TED.2006.874089.

- 4. Chen J., Liou J. J. On-Chip Spiral Inductors for RF Applications: An Overview // Journal of Semiconductor Technology and Science. 2004. Vol. 4,  $N_2$  3. P. 149-167.

- 5. Liang H.-B., Lin Y.-S., Chen C.-C. [et al.]. Optimization of PGS Pattern of Transformers/Inductors in Standard RF BiCMOS Technology for RFIC Applications // Radio Frequency Integrated Circuits (RFIC) Symposium, 2006 IEEE. 2006. 4 p. DOI: 10.1109/PEIC 2006.1651205

- 6. Royet A. S., Barbé J. C., Valorge O. [et al.]. Constant. Experimental and Simulation Results on Si Integrated Inductor Efficiency for Smart RF-ICs // 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS). 2014. P. 368—370. DOI: 10.1109/ICECS.2014.7049998.

- 7. Shi J., Yin W.-Y., Liao H. [et al.]. The Enhancement of Q Factor for Patterned Ground Shield Inductors at High Temperatures // IEEE Transactions on Magnetics.2006. Vol. 42, Issue 7. P. 1873 1875. DOI: 10.1109/TMAG.2006.874186.

- 8. Zhang Z., Liao X. Micromachined GaAs MMIC-Based Spiral Inductors With Metal Shores and Patterned Ground Shields // IEEE Sensors Journal. 2012. Vol. 12, Issue 6. P. 1853—1860. DOI: 10.1109/JSEN.2011.2178066.

- 9. Kaynak M., Korndörfer F., Wipf C. [et al.]. High-Q passives for mm-wave SiGe applications // IEEE Bipolar/BiCMOS Circuits and Technology Meeting. 2009. P. 194-197. DOI: 10.1109/BIPOL.2009.5314243.

- 10. López-Villegas J. M., Samitier J., Cane C. [et al.]. Bausells. Improvement of the Quality Factor of RF Integrated Inductors by Layout Optimization // IEEE Transactions on Microwave Theory and Techniques. 2000. Vol. 48, Issue 1. P. 76-83. DOI: 10.1109/22.817474.

- 11. Korndörfer F., Kaynak M., Mühlhaus V. Simulation and Measurement of Back Side Etched Inductors // The 5th European Microwave Integrated Circuits Conference. 2010. P. 389 392.

- 12. Ерохин В. В. Верификация модели интегральной катушки индуктивности для СВЧ LC-фильтров в Si- и SiGeсистемах на кристалле // Вестник СибГУТИ. 2022. № 2 (58). С. 94—109. DOI: 10.55648/1998-6920-2022-16-2-94-109.

- 13. Ерохин В. В., Садыков Ж. Б., Блинков С. Д. Влияние топологии общего вывода на АЧХ интегрального СВЧ LС-фильтра // Динамика систем, механизмов и машин. 2022. Т. 10, № 2. С. 57—64. DOI: 10.25206/2310-9793-2022-10-2-57-64.

- 14. Ruehli A. E., Antonini G., Jiang L. Skin-Effect Model for Round Wires in PEEC. International Symposium on Electromagnetic Compatibility EMC EUROPE. 2012. P. 1—6. DOI:10.1109/EMCEurope.2012.6396927.

- 15. Chan R.-J., Guo J.-C. Analysis and Modeling of Skin and Proximity Effects for Millimeter-Wave Inductors Design in Nanoscale Si CMOS // 9th European Microwave Integrated Circuit Conference. 2014. P. 13–16. DOI: 10.1109/EuMIC.2014.

- 16. Koutsoyannopoulos Y. K., Papananos Y. Systematic Analysis and Modeling of Integrated Inductors and Transformers in RF IC Design // IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing. 2000. Vol. 47, Issue 8. P. 699–713. DOI: 10.1109/82.861403.

- 17. Chen J., Liou J. J. On-Chip Spiral Inductors for RF Applications: An Overview // Journal of Semiconductor Technology and Science. 2004. P. 149-167.

- 18. Shaltout A. H., Gregori S. Optimizing the Inductance Time-Constant Ratio of Polygonal Integrated Inductors // IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS). 2018. P. 448-451. DOI: 10.1109/MWSCAS.2018.8623945.

- 19. Hsu H.-M., Chang J.-Z., Chien H.-C. Coupling Effect of On-Chip Inductor With Variable Metal Width // IEEE Microwave and Wireless Components Letters. 2007. Vol. 17, Issue 7. P. 498 500. DOI: 10.1109/LMWC.2007.899306.

- 20. Elsaadi M., Tayel M. B., Steenson D. P. An Empirical Formula of Fringing Field Capacitance for MEMS Tunable Capacitor Actuators // IEEE 1st International Maghreb Meeting of the Conference on Sciences and Techniques of Automatic Control and Computer Engineering MI-STA. 2021. P. 674–678. DOI:10.1109/MI-STA52233.2021.9464509.

- 21. Goni A., del Pino J., Gonzalez B. [et al.]. An Analytical Model of Electric Substrate Losses for Planar Spiral Inductors on Silicon // IEEE Transactions on Electron Devices. 2007. Vol. 54, Issue 3. P. 546 553. DOI: 10.1109/TED.2006.890366.

- 22. Sathyasree J., Vanukuru V., Nair D. R. [et al.]. A Substrate Model for On-Chip Tapered Spiral Inductors With Forward and Reverse Excitations // IEEE Transactions on Electron Devices. 2019. Vol. 66, Issue 1. P. 4. DOI: 10.1109/TED.2018.2873796.

- 23. Зааль Р. Справочник по расчету фильтров: пер. с нем. Москва: Радио и связь, 1983. 752 с.

- 24. Ханзел Г. Е. Справочник по расчету фильтров: пер. с англ. / под ред. А. Е. Знаменского. Москва: Советское радио, 1974. 288 с.

- 25. Татур Т. А. Основы теории электрических цепей. Москва: Высшая школа. 1980. 271 с.

- 26. Ерохин В. В., Завьялов С. А. Автоматизированный синтез топологий СВЧ интегральных высокоизбирательных LС-фильтров с минимизацией потерь в полосе пропускания: программа для ЭВМ. Москва: ФИПС, 2023. № 2023660979.

- 27. Ahyoune S., López-Villegas J., Sieiro J. [et al.]. Effects of Shielding Structures on the Performance of Planar Inductors // Conference on Design of Circuits and Integrated Systems (DCIS). 2016. DOI: 10.1109/DCIS.2016.7845353.

- 28. Ali M. H. M., Ler C.-L., Rustagi S. C. [et al.]. The Impact of Electromagnetic Coupling of Guard Ring Metal Lines on the Performance of On-chip Spiral Inductor in Silicon CMOS // 2nd Asia Symposium on Quality Electronic Design (ASQED). 2010. P. 285 288. DOI: 10.1109/ASQED.2010.5548257.

- 29. Kojima K., Ohguro T., Momose H. S. [et al.]. Guardring design for high-performance RF CMOS // International

Conference on Solid State Devices and Materials. 2002. P. 400 – 401. DOI: 10.7567/SSDM.2002.P2-9.

30. Pun A., Yeung T., Lau J. [et al.]. Experimental Results and Simulation of Substrate Noise Coupling via Planar Spiral Inductor in RF ICs // International Electron Devices Meeting. IEDM Technical Digest. 1997. P. 325—328. DOI: 10.1109/IEDM.1997.650393.

**ЕРОХИН Виктор Валерьевич,** аспирант кафедры «Радиотехнические устройства и системы диагностики», научный сотрудник научно-исследовательской лаборатории «Системы на кристалле» Омского государственного технического университета (ОмГТУ), г. Омск.

SPIN-код: 4231-2673 AuthorID (РИНЦ): 918830

Адрес для переписки: viktor\_erohin@mail.ru

ЗАВЬЯЛОВ Сергей Анатольевич, кандидат технических наук, доцент (Россия), доцент кафедры «Радио-

технические устройства и системы диагностики», старший научный сотрудник научно-исследовательской лаборатории «Системы на кристалле» ОмГТУ, г. Омск.

SPIN-код: 6758-0406

ORCID: 0000-0001-5114-2074 AuthorID (SCOPUS): 57221599219 ResearcherID: E-8661-2014

Адрес для переписки: zavyalov62@mail.ru

#### Для цитирования

Ерохин В. В., Завьялов С. А. Автоматизированный синтез топологий интегральных сверхвысокочастотных LС-фильтров с минимизацией потерь в полосе пропускания // Омский научный вестник. 2023. № 4 (188). С. 152—161. DOI: 10.25206/1813-8225-2023-188-152-161.

Статья поступила в редакцию 13.04.2023 г. © В. В. Ерохин, С. А. Завьялов

UDC 621.372.54

DOI: 10.25206/1813-8225-2023-188-152-161

**EDN: OJPIEK**

V. V. EROKHIN S. A. ZAVYALOV

> Omsk State Technical University, Omsk, Russia

## AUTOMATED SYNTHESIS OF INTEGRATED MICROWAVE LC-FILTERS LAYOUTS WITH PASSBAND LOSSES MINIMIZATION

The paper proposes the developed technique for automated synthesis of integrated microwave LC filter layouts with passband losses minimization by minimizing interconnection lengths and searching for optimal layouts of conductors, inductors, and capacitors. Algorithms for minimizing losses and length of LC-filter interconnections are proposed. The layouts of conductors, inductors, and capacitors are optimized based on silicon-verified models that take into account the main characteristics and limitations of the process, skin effect, edge effects, substrate and via influences. The CAD is developed in MathCAD software based on the proposed technique. The use of CAD made it possible to reduce the engineering time for integrated LC-filters to tens of minutes, reduce the filters passband losses by 1,1–2,7 dB and increase the AFCs gain slope by 47–267 dB/dec.

Keywords: microwave, SoC, filter synthesis, LC-filter, MathCAD, optimization algorithm, technique.

#### References

- 1. Kim J., Plouchart J. K., Zamdmer N. [et al.]. High-Performance Three-Dimensional On-chip Inductors in SOI CMOS Technology for Monolithic RF Circuit Applications // Radio Frequency Integrated Circuits (RFIC) Symposium, 2003 IEEE. 2003. P. 591 594. DOI: 10.1109/RFIC.2003.1214016. (In Engl.).

- 2. Danesh M., Long J. R. Differentially Driven Symmetric Microstrip Inductors // IEEE Transactions on Microwave Theory and Techniques. 2002. Vol. 50, Issue 1. P. 332-341. DOI: 10.1109/22.981285. (In Engl.).

- 3. Chen J., Liou J. J. Improved and Physics-Based Model for Symmetrical Spiral Inductors // IEEE Transactions on Electron

Devices. 2006. Vol. 53, Issue 6. P. 1300-1309. DOI: 10.1109/ TED.2006.874089. (In Engl.).

- 4. Chen J., Liou J. J. On-Chip Spiral Inductors for RF Applications: An Overview // Journal of Semiconductor Technology and Science. 2004. Vol. 4, no. 3. P. 149-167. (In Engl.).

- 5. Liang H.-B., Lin Y.-S., Chen C.-C. [et al.]. Optimization of PGS Pattern of Transformers/Inductors in Standard RF BiCMOS Technology for RFIC Applications // Radio Frequency Integrated Circuits (RFIC) Symposium, 2006 IEEE. 2006. 4 p. DOI: 10.1109/RFIC.2006.1651205. (In Engl.).

- 6. Royet A. S., Barbé J. C., Valorge O. [et al.]. Constant. Experimental and Simulation Results on Si Integrated Inductor

Efficiency for Smart RF-ICs // 21st IEEE International Conference on Electronics, Circuits and Systems (ICECS). 2014. P. 368-370. DOI: 10.1109/ICECS.2014.7049998. (In Engl.).

- 7. Shi J., Yin W.-Y., Liao H. [et al.]. The Enhancement of Q Factor for Patterned Ground Shield Inductors at High Temperatures // IEEE Transactions on Magnetics.2006. Vol. 42, Issue 7. P. 1873—1875. DOI: 10.1109/TMAG.2006.874186. (In Engl.).

- 8. Zhang Z., Liao X. Micromachined GaAs MMIC-Based Spiral Inductors With Metal Shores and Patterned Ground Shields // IEEE Sensors Journal. 2012. Vol. 12, Issue 6. P. 1853—1860. DOI: 10.1109/JSEN.2011.2178066. (In Engl.).

- 9. Kaynak M., Korndörfer F., Wipf C. [et al.]. High-Q passives for mm-wave SiGe applications // IEEE Bipolar/BiCMOS Circuits and Technology Meeting. 2009. P. 194–197. DOI: 10.1109/BIPOL.2009.5314243. (In Engl.).

- 10. López-Villegas J. M., Samitier J., Cane C. [et al.]. Bausells. Improvement of the Quality Factor of RF Integrated Inductors by Layout Optimization // IEEE Transactions on Microwave Theory and Techniques. 2000. Vol. 48, Issue 1. P. 76–83. DOI: 10.1109/22.817474. (In Engl.).

- 11. Korndörfer F., Kaynak M., Mühlhaus V. Simulation and Measurement of Back Side Etched Inductors // The 5th European Microwave Integrated Circuits Conference. 2010. P. 389-392. (In Engl.).

- 12. Erokhin V. V. Verifikatsiya modeli integral'noy katushki induktivnosti dlya SVCh LC-fil'trov v Si- i SiGe-sistemakh na kristalle [Integrated Inductor Model Verification for Microwave LC-filters in Si and SiGe Systems on a Chip] // Vestnik SibGUTI. The Herald of the Siberian State University of Telecommunications and Information Science. 2022. No. 2 (58). P. 94–109. DOI: 10.55648/1998-6920-2022-16-2-94-109. (In Russ.).

- 13. Erokhin V. V., Sadykov Zh. B., Blinkov S. D. Vliyaniye topologii obshchego vyvoda na AChKh integral'nogo SVCh LC-fil'tra [Ground conductor layout influence on integrated microwave LC-filter AFCS] // Dinamika sistem, mekhanizmov i mashin. *Dynamics of Systems, Mechanisms and Machines.* 2022. Vol. 10, no. 2. P. 57–64. DOI: 10.25206/2310-9793-2022-10-2-57-64. (In Russ.).

- 14. Ruehli A. E., Antonini G., Jiang L. Skin-Effect Model for Round Wires in PEEC. International Symposium on Electromagnetic Compatibility EMC EUROPE. 2012. P. 1-6. DOI: 10.1109/EMCEurope.2012.6396927. (In Engl.).

- 15. Chan R.-J., Guo J.-C. Analysis and Modeling of Skin and Proximity Effects for Millimeter-Wave Inductors Design in Nanoscale Si CMOS // 9th European Microwave Integrated Circuit Conference. 2014. P. 13–16. DOI: 10.1109/EuMIC.2014.6997779. (In Engl.).

- 16. Koutsoyannopoulos Y. K., Papananos Y. Systematic Analysis and Modeling of Integrated Inductors and Transformers in RF IC Design // IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing. 2000. Vol. 47, Issue 8. P. 699 713. DOI: 10.1109/82.861403. (In Engl.).

- 17. Chen J., Liou J. J. On-Chip Spiral Inductors for RF Applications: An Overview // Journal of Semiconductor Technology and Science. 2004. P. 149-167. (In Engl.).

- 18. Shaltout A. H., Gregori S. Optimizing the Inductance Time-Constant Ratio of Polygonal Integrated Inductors // IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS). 2018. P. 448-451. DOI: 10.1109/MWSCAS.2018.8623945. (In Engl.).

- 19. Hsu H.-M., Chang J.-Z., Chien H.-C. Coupling Effect of On-Chip Inductor With Variable Metal Width // IEEE Microwave and Wireless Components Letters. 2007. Vol. 17, Issue 7. P. 498 500. DOI: 10.1109/LMWC.2007.899306. (In Engl.).

- 20. Elsaadi M., Tayel M. B., Steenson D. P. An Empirical Formula of Fringing Field Capacitance for MEMS Tunable Capacitor Actuators // IEEE 1st International Maghreb Meeting of the Conference on Sciences and Techniques of Automatic

- Control and Computer Engineering MI-STA. 2021. P. 674 678. DOI:10.1109/MI-STA52233.2021.9464509. (In Engl.).

- 21. Goni A., del Pino J., Gonzalez B. [et al.]. An Analytical Model of Electric Substrate Losses for Planar Spiral Inductors on Silicon // IEEE Transactions on Electron Devices. 2007. Vol. 54, Issue 3. P. 546 553. DOI: 10.1109/TED.2006.890366. (In Engl.).

- 22. Sathyasree J., Vanukuru V., Nair D. R. [et al.]. A Substrate Model for On-Chip Tapered Spiral Inductors With Forward and Reverse Excitations // IEEE Transactions on Electron Devices. 2019. Vol. 66, Issue 1. P. 4. DOI: 10.1109/TED.2018.2873796. (In Engl.).

- 23. Zaal R. Spravochnik po raschetu fil'trov [Handbook of filter design]: trans from Germ. Moscow, 1983, 752 p. (In Russ.).

- 24. Khanzel G. E. Spravochnik po raschetu fil'trov [Handbook of filter design]: trans from Engl. / ed by A. E. Znamenskogo. Moscow, 1974. 288 p. (In Russ.).

- 25. Tatur T. A. Osnovy teorii elektricheskikh tsepey [Fundamentals of the electrical circuits theory]. Moscow, 1980. 271 p. (In Russ.).

- 26. Erokhin V. V., Zav'yalov S. A. Avtomatizirovannyy sintez topologiy SVCh integral'nykh vysokoizbiratel'nykh LC-fil'trov s minimizatsiyey poter' v polose propuskaniya: programma dlya EVM [Automated synthesis of microwave topologies of integrated highly selective LC filters with minimisation of losses in the passband: computer program]. Moscow, 2023. No. 2023660979. (In Russ.)

- 27. Ahyoune S., Lypez-Villegas J., Sieiro J. [et al.]. Effects of Shielding Structures on the Performance of Planar Inductors // Conference on Design of Circuits and Integrated Systems (DCIS). 2016. DOI: 10.1109/DCIS.2016.7845353. (In Engl.).

- 28. Ali M. H. M., Ler C.-L., Rustagi S. C. [et al.]. The Impact of Electromagnetic Coupling of Guard Ring Metal Lines on the Performance of On-chip Spiral Inductor in Silicon CMOS // 2nd Asia Symposium on Quality Electronic Design (ASQED). 2010. P. 285 288. DOI: 10.1109/ASQED.2010.5548257. (In Engl.).

- 29. Kojima K., Ohguro T., Momose H. S. [et al.]. Guardring design for high-performance RF CMOS // International Conference on Solid State Devices and Materials. 2002. P. 400 401. DOI: 10.7567/SSDM.2002.P2-9. (In Engl.).

- 30. Pun A., Yeung T., Lau J. [et al.]. Experimental Results and Simulation of Substrate Noise Coupling via Planar Spiral Inductor in RF ICs // International Electron Devices Meeting. IEDM Technical Digest. 1997. P. 325–328. DOI: 10.1109/IEDM.1997.650393. (In Engl.).

**EROKHIN Viktor Valerievich,** Graduate Student of Radio Devices and Diagnostic Systems Department, Research Scientist of «Systems on Chip» Research Laboratory, Omsk State Technical University (OmSTU), Omsk.

SPIN-code: 4231-2673 AuthorID (RSCI): 918830

Correspondence address: viktor\_erohin@mail.ru

**ZAVYALOV Sergey Anatolyevich,** Associate Professor of Technical Sciences, Associate Professor of Radio Devices and Diagnostic Systems Department, Senior Research of «Systems on Chip» Research Laboratory, OmSTU, Omsk.

Correspondence address: zavyalov62@mail.ru

#### For citations

Erokhin V. V., Zavyalov S. A. Automated synthesis of integrated microwave LC-filters layouts with passband losses minimization // Omsk Scientific Bulletin. 2023. No. 4 (188). P. 152-161. DOI: 10.25206/1813-8225-2023-188-152-161.

Received April 13, 2023. © V. V. Erokhin, S. A. Zavyalov